# Digital Gate Driver IC with Fully Integrated Automatic Timing Control Function in Stop-and-Go Gate Drive for IGBTs

Dibo Zhang, Kohei Horii, Katsuhiro Hata, and Makoto Takamiya The University of Tokyo, Tokyo, Japan

Abstract— To reduce loss and noise during switching of IGBTs at low cost even under changing operating conditions, namely load current (IL) and junction temperature (TJ) variation, the world's first active digital gate driver IC with fully integrated automatic timing control function that achieves both single-chip integration and real-time control is developed. In order to handle various IGBTs with one type of gate driver, the proposed IC also has the world's first 6-bit programmable gate current function in the closed-loop active gate drivers. In the double pulse test of IGBT, compared with the conventional single-step gate drive, the stop-and-go gate drive with automatic timing control using the proposed IC effectively reduces the switching loss (ELOSS) under the collector current overshoot (IOVERSHOOT)-aligned condition and reduces IOVERSHOOT under ELOSS-aligned condition with IL ranging from 10 A to 80 A and T<sub>J</sub> ranging from 25 °C (room temperature) to 125 °C, and particularly at the condition of  $I_{\rm L}$  = 80 A at 25 °C, the proposed gate driver reduces ELOSS by 49 % under the IOVERSHOOT-aligned condition and reduces IOVERSHOOT by 33 % under the ELOSSaligned condition.

Keywords— IGBT, IC, surge current, energy loss, active gate driver

## I. INTRODUCTION

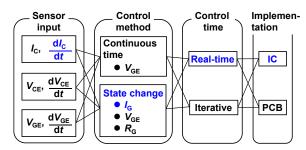

A lot of active gate drivers (AGDs), where the gate driving waveform is controlled during the turn-on/off transients, have been proposed to reduce both the switching loss and the switching noise of power devices. AGDs can be classified into two types, open-loop control [1-6] and closed-loop control [7-19, 22]. The closed-loop AGDs are required instead of the open-loop AGDs, because the optimal driving waveform changes depending on the operating conditions (e.g. load current and temperature) [20]. Fig. 1 summarizes the design choices in conventional closed-loop AGDs. To make the closed-loop AGDs practical, the following three points are required: (1) single-chip integration instead of PCB implementation for lower cost, (2) real-time control instead of iterative control to reliably handle dynamic change of operating conditions, and (3) programmable AGDs instead of fixed-function AGDs that require individual optimization for different product variety of power devices. In the closed-loop

Fig. 1: Design choices in closed-loop AGDs. This work is shown in blue.

AGDs, however, no previous paper has realized (1) and (2) simultaneously, and no previous paper on (3) has been published. To solve the problems, in this paper, a digital gate driver (DGD) IC with fully integrated automatic timing control (ATC) function for IGBTs that realizes all of (1) to (3) is proposed. The design choices in this paper are shown in blue in Fig. 1.

## II. PROPOSED DIGITAL GATE DRIVER IC WITH AUTOMATIC TIMING CONTROL

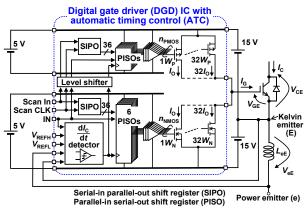

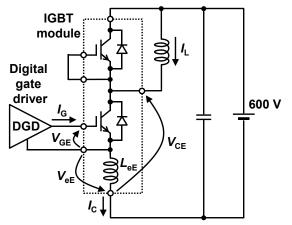

Figs. 2 and 3 show a circuit schematic and a timing chart of the proposed DGD IC with ATC, respectively. In the following, turn-on is discussed, whereas the exact same is true for turn-off. The IC includes  $dI_C/dt$  detector for the state change, controller for ATC, and a 6-bit current-source type

Fig. 2: Circuit schematic of proposed DGD IC with ATC

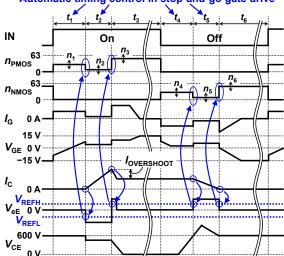

Fig. 3: Timing chart of proposed DGD IC with ATC.

digital gate driver with variable gate current  $(I_G)$  in 64 levels, where  $I_{\rm G} = n_{\rm PMOS} \times 48$  mA and  $n_{\rm PMOS}$  is an integer from 0 to 63 (max  $I_G = 3A$ ). At turn-on, an active gate driving is performed in three slots from  $t_1$  to  $t_3$  with different  $I_G$  of strong  $(n_1)$ -weak  $(n_2)$ -strong  $(n_3)$ , and this driving method is defined as stop-and-go gate drive (SGGD) [21]. I<sub>G</sub> switching is realized by a digital timing control input from  $dI_C/dt$  detector to parallel-in serial-out registers (PISO) to drive nMOSFETs and pMOSFETs with different gate widths connected in parallel.  $n_1$  to  $n_3$  are preset by a digital input (Scan In), while  $t_1$  and  $t_2$  are automatically determined by ATC. An important feature of this IC is the full integration of  $t_1$  and  $t_2$  real-time automatic control functions on a single chip. The real-time control of  $t_1$  and  $t_2$  is done by detecting  $dI_{C}/dt$  by sensing the voltage ( $V_{eE}$ ) of the parasitic inductance ( $L_{eE}$ ) between Kelvin emitter and power emitter in Fig. 2, because  $V_{eE} = -L_{eE}$  $(dI_C/dt)$ , where  $I_C$  is the collector current. Specifically, as shown in Fig. 3, the end timing of  $t_1$  is determined by detecting the negative  $V_{eE}$  at the beginning of  $I_C$  flow using a comparator with the reference voltage of  $V_{\text{REFL}}$ , and the end timing of  $t_2$  is determined by detecting the positive  $V_{eE}$  at the timing immediately after I<sub>C</sub> overshoots using a comparator with the reference voltage of  $V_{\text{REFH}}$ . Similarly, at turn-off,  $t_4$  to  $t_6$  is also automatically switched by the comparing the reference voltage with  $V_{eE}$  completed by  $dI_{C}/dt$  detector.

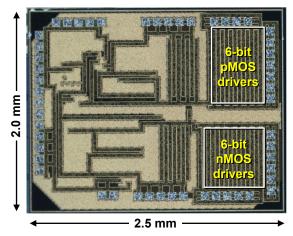

Fig. 4 shows a die photo of DGD IC with ATC fabricated with 180-nm BCD process. The die size is 2.0 mm by 2.5 mm.

Fig. 4: Die photo of DGD IC with ATC.

#### III. MEASURED RESULTS

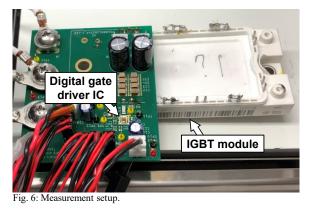

Figs. 5 and 6 show a circuit schematic and a measurement setup of the double pulse test using the developed DGD IC and an IGBT module (FS100R12N2T4, 1200 V, 100 A), respectively. The IGBT module is placed on a hotplate for measurement under different temperature. In this paper, only turn-on measurements are discussed, and turn-off measurements are not discussed, because, in the IGBT module, no trade-off relationship between the turn-off loss and the collector-to-emitter voltage overshoot was observed when  $I_G$ of DGD IC was varied.

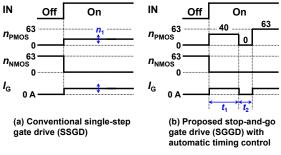

Figs. 7 (a) and (b) show the timing charts for turn-on of the conventional single-step gate drive (SSGD) and the proposed SGGD for comparison, respectively. In SSGD,  $n_1$  is varied from 4 to 63, which emulates a conventional gate driver with varied gate resistance. In SGGD, on the other hand,  $(n_1, n_2, n_3)$  are preset to (40, 0, 63), a set of parameters where

Fig. 5: Circuit schematic of double pulse test.

Fig. 7: Timing charts for turn-on.

$I_{\text{OVERSHOOT}}$  is optimally suppressed with the weakest driving forced "0", and follow-up turning-on is returned with the greatest driving force "63" to maximumly reduce further energy loss, and  $t_1$  and  $t_2$  are automatically determined by ATC.

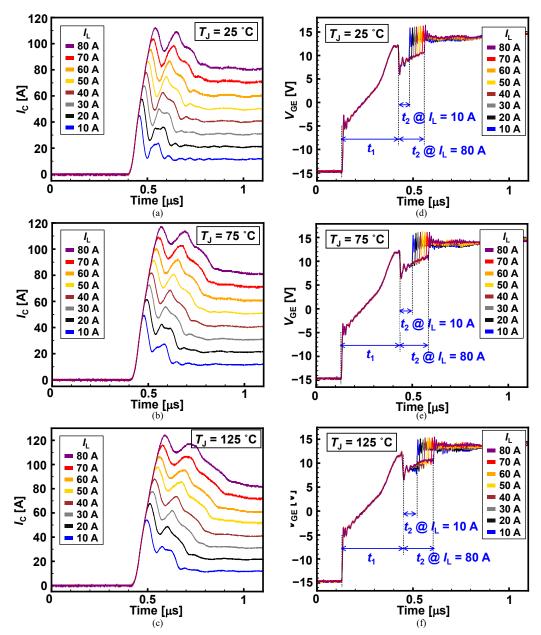

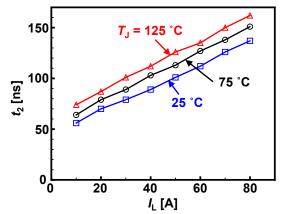

Figs. 8 (a) to (c) show the measured  $I_{\rm C}$  and Figs. 8 (d) to (f) show the gate-emitter voltage ( $V_{\rm GE}$ ) waveforms in SGGD with ATC with varied load current ( $I_{\rm L}$ ) from 10 A to 80 A, and junction temperature ( $T_{\rm J}$ ) of 25 °C, 75 °C (IC average temperature 60 °C), and 125 °C (IC average temperature 90 °C), respectively.  $V_{\rm GE}$  waveforms explicitly show the sunken parts, which represent  $t_2$ , varied in duration corresponding to variation in  $I_{\rm L}$  for each of the three  $T_{\rm J}$ 's measured, and  $t_1$  remains the same within each  $T_{\rm J}$ . Fig. 9 shows the measured  $t_2$  vs.  $I_{\rm L}$  relationship of the three sets of data in different  $T_{\rm J}$ .  $t_2$  is automatically increased by ATC, and it is clearly observed that as  $t_2$  increases approximately linearly with  $I_{\rm L}$  when  $T_{\rm J}$  is

Fig. 8: Measured results in SGGD with ATC with varied  $I_{\rm L}$  and  $T_{\rm J}$ . (a) to (c) are  $I_{\rm C}$  waveforms. (d) to (f) are  $V_{\rm GE}$  waveforms. (a) and (d) for  $T_{\rm J} = 25$  °C. (b) and (e) for  $T_{\rm J} = 75$  °C. (c) and (f) for  $T_{\rm J} = 125$  °C.

the same. On the other hand, for a fixed  $I_{\rm L}$ ,  $t_2$  duration increases as  $T_{\rm J}$  increases, because according to the characteristics of the IGBT module under test,  $I_{\rm OVERSHOOT}$ increases as  $T_{\rm J}$  increases. Therefore, the proposed gate driver automatically extend the weaker driving slot ( $t_2$ ) to suppress the surge current.

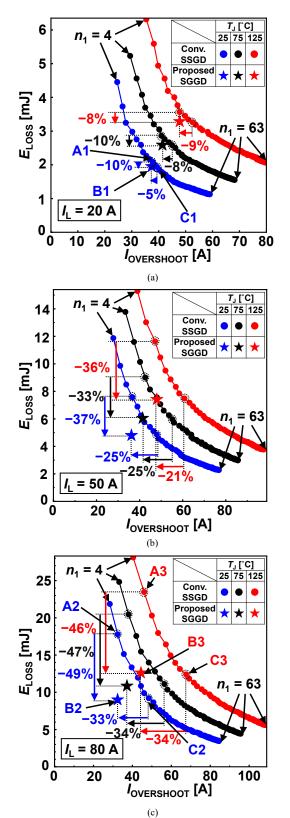

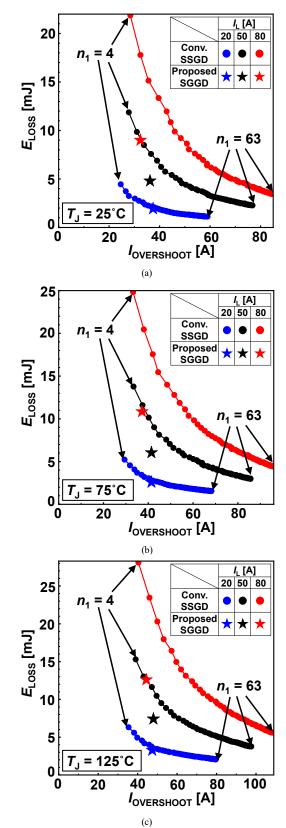

Figs. 10 (a) to (c) show the measured switching loss ( $E_{LOSS}$ ) vs. the collector current overshoot ( $I_{OVERSHOOT}$ ) of the conventional SSGD and the proposed SGGD at  $I_L = 20$  A, 50 A, and 80 A, respectively. In each graph,  $T_J$  is varied to 25 °C, 75 °C, and 125 °C. The red curve, which represents  $T_J = 125$  °C, black curve, which represents  $T_J = 75$  °C, and blue curve, which represents  $T_J = 25$ °C, show the trade-off curves of the conventional SSGD with varied  $n_I$  from 4 to 63. In all cases, the proposed SGGD has lower  $E_{LOSS}$  and lower  $I_{OVERSHOOT}$

Fig. 9: Measured  $t_2$  vs.  $I_L$  at  $T_J = 25$  °C, 75 °C, and 125 °C.

Fig. 11: Measured  $E_{\text{LOSS}}$  vs.  $I_{\text{OVERSHOOT}}$  of conventional SSGD and proposed SGGD at  $T_{\text{J}} = 25$  °C (a), 75 °C (b), and 125 °C (c), and each varies in  $I_{\text{L}}$ .

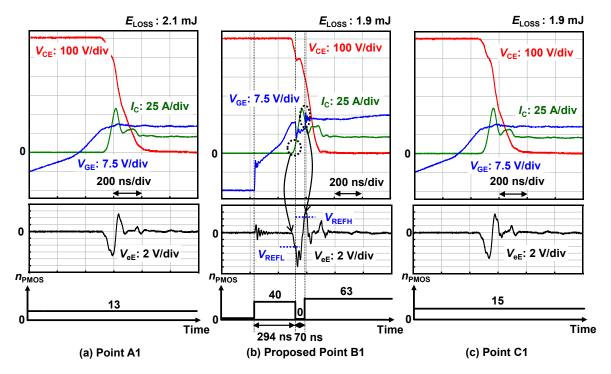

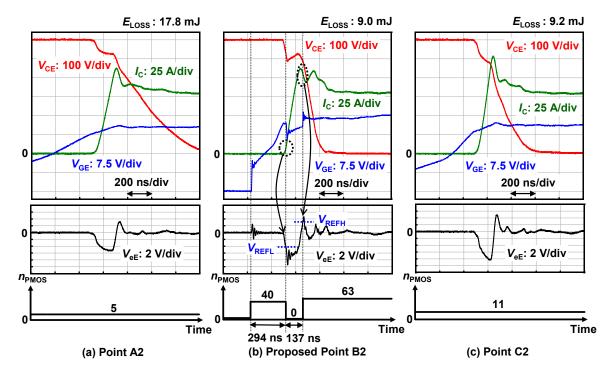

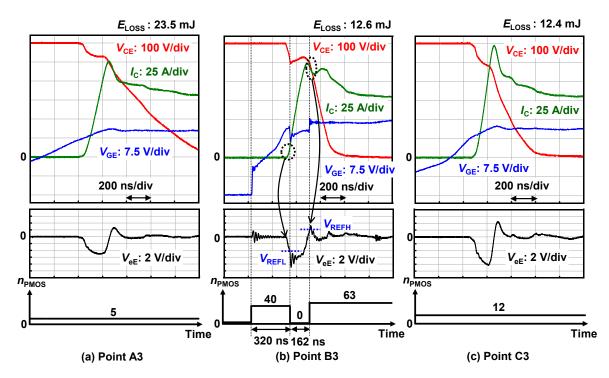

than the conventional SSGD. In Figs. 10 (a) and (c), Points A1 to A3, Points B1 to B3, and Points C1 to C3 are defined for ( $I_L$ ,  $T_J$ ) = (20 A, 25 °C), (80 A, 25 °C), and (80 A, 125 °C), respectively, where Points "B"s are the proposed SGGD, Point "A"s are the conventional SSGD with closest  $I_{OVERSHOOT}$  comparing to proposed ones, and Point "C"s are the conventional SSGD with the closest  $E_{LOSS}$  comparing to

proposed ones. The measured waveforms for these nine points are shown later in Figs. 12 to 14. At  $(I_L, T_J) = (20 \text{ A}, 25 \degree \text{C})$  in Fig. 10 (a), compared with the conventional SSGD (Point A1 and Point C1), the proposed SGGD (Point B1) reduces  $E_{\text{LOSS}}$ by 10 % under  $I_{\text{OVERSHOOT}}$ -aligned condition and reduces  $I_{\text{OVERSHOOT}}$  by 5 % under  $E_{\text{LOSS}}$ -aligned condition. At  $(I_L, T_J) =$ (80 A, 25 °C) in Fig. 10 (c), compared with the conventional

Fig. 12: Measured waveforms in Point A1, Proposed Point B1, and Point C1 in Fig. 10 (a) at  $I_L = 20$  A and  $T_J = 25$ °C.

Fig. 13: Measured waveforms in Point A2, Proposed Point B2, and Point C2 in Fig. 10 (c) at  $I_L = 80$  A and  $T_J = 25$  °C.

Fig. 14: Measured waveforms in Point A3, Proposed Point B3, and Point C3 in Fig. 10 (c) at  $I_{\rm L} = 80$  A and  $T_{\rm J} = 125^{\circ}$ C.

SSGD (Point A2 and Point C2), the proposed SGGD (Point B2) reduces  $E_{\text{LOSS}}$  by 49 % under  $I_{\text{OVERSHOOT}}$ -aligned condition and reduces  $I_{\text{OVERSHOOT}}$  by 33 % under  $E_{\text{LOSS}}$ -aligned condition. At  $(I_{\text{L}}, T_{\text{J}}) = (80 \text{ A}, 125 \text{ °C})$  in Fig. 10 (c), compared with the conventional SSGD (Point A3 and Point C3), the proposed SGGD (Point B3) reduces  $E_{\text{LOSS}}$  by 46 % under  $I_{\text{OVERSHOOT}}$ -aligned condition and reduces  $I_{\text{OVERSHOOT}}$  by 34 % under  $E_{\text{LOSS}}$ -aligned condition.

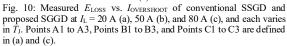

Figs. 11 (a) to (c), on the other hand, show the measured  $E_{\text{LOSS}}$  vs.  $I_{\text{OVERSHOOT}}$  of the conventional SSGD and the proposed SGGD at  $T_1 = 25$  °C, 75 °C, and 125 °C, respectively. In each graph,  $I_{\text{L}}$  is varied to 20 A, 50 A, and 80 A. Similarly, in each graph, The red curve, which represents  $I_{\text{L}} = 80$  A, black curve, which represents  $I_{\text{L}} = 50$  A, and blue curve, which represents  $I_{\text{L}} = 20$  A, show the trade-off curves of the conventional SSGD with varied  $n_1$  from 4 to 63, and the proposed SGGD has advantage over conventional SSGD on lower  $E_{\text{LOSS}}$  and lower  $I_{\text{OVERSHOOT}}$ .

Figs. 12 (a) to (c) show the measured waveforms in Point A1, which represents the waveform of SGGD with  $n_1 = 13$ , Point B1, the proposed SGGD, and Point C1, which represents the waveform of SGGD with  $n_1 = 15$  in Fig. 10 (a), respectively, under  $I_{\rm L} = 20$  A,  $T_{\rm J} = 25^{\circ}$ C condition. In Fig. 12 (b), SGGD is realized with  $t_1$  and  $t_2$  correctly controlled by detecting  $V_{eE}$  comparing to  $V_{REFH}$  and  $V_{REFL}$ . Figs. 13 (a) to (c) show the measured waveforms in Point A2, B2, and C2 in Fig. 10 (c), as SGGD with  $n_1 = 5$ , the proposed SGGD, and SGGD with  $n_1 = 11$ , respectively, under  $I_L = 80$  A,  $T_J = 25^{\circ}$ C condition, regarded as the standard condition, commonly loaded by the IGBT device. Fig. 13 (b) clearly shows that the start of  $I_{\rm C}$  flow and  $I_{\rm C}$  overshoot are properly detected by  $V_{\rm eE}$ . Similarly, Figs. 14 (a) to (c) show the measured waveforms in Point A3, B3, and C3, as SGGD with n1 = 5, the proposed SGGD, and SGGD with  $n_1 = 12$ , respectively, under  $I_L = 80$  A,  $T_J = 125$ °C condition. In Fig. 14 (b), automatic control of  $t_1$  and  $t_2$  has

TABLE I. COMPARISON TABLE OF CLOSED-LOOP AGDS

|                                          | TPEL'15                                          | TPEL'18                                          | TPEL'21                      | ISSCC'19                      | ISSCC'21                                        | This work                    |

|------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------------------|-------------------------------|-------------------------------------------------|------------------------------|

|                                          | [11]                                             | [12]                                             | [14]                         | [13]                          | [18]                                            | THIS WORK                    |

| Target power<br>device                   | IGBT                                             | IGBT                                             | SiC<br>MOSFET                | SI MOSFET                     | GaN FET                                         | IGBT                         |

| Sensor input                             | d/ <sub>c</sub> / d <i>t,</i><br>V <sub>CE</sub> | d/ <sub>C</sub> / d <i>t,</i><br>V <sub>CE</sub> | d <i>l<sub>c</sub> / dt</i>  | V <sub>DS</sub>               | V <sub>DD</sub> of high-<br>side gate<br>driver | d/ <sub>c</sub> / dt         |

| Feedback control target                  | V <sub>GE</sub><br>wavefor<br>m                  | Timing of<br>state<br>change                     | Timing of<br>state<br>change | Timing of<br>state<br>change  | Timing of<br>state<br>change                    | Timing of<br>state<br>change |

| Real-time control                        | Yes                                              | Yes                                              | Yes                          | No                            | No                                              | Yes                          |

| Number of states<br>per switching        |                                                  | 4                                                | 3                            | 3                             | 3                                               | 3                            |

| Preset parameters<br>for each state      |                                                  | I <sub>G</sub>                                   | V <sub>gs</sub>              | R <sub>G</sub>                | I <sub>G</sub>                                  | I <sub>G</sub>               |

| Levels of<br>parameter                   |                                                  | NA                                               | 2                            | 2                             | 3                                               | 6 bit                        |

| Implementation                           | РСВ                                              | РСВ                                              | РСВ                          | IC (Not fully<br>integrated)* | IC (Fully<br>integrated)                        | IC (Fully<br>integrated)     |

| IC Process                               |                                                  |                                                  |                              | 130 nm<br>HV CMOS             | 500 nm,<br>600 V SOI**                          | 180 nm<br>BCD                |

| *Voltage divider for V is not integrated |                                                  |                                                  |                              |                               |                                                 |                              |

\*Voltage divider for  $V_{\rm DS}$  is not integrated. \*\*High-voltage IC process with the same breakdown voltage as  $V_{\rm CC}$  of main circuit is required.

been successfully achieved by detecting  $V_{eE}$  comparing to  $V_{REFH}$  and  $V_{REFL}$ . Note also that comparing  $t_1$  in Fig. 13 (b) and Fig. 14 (b), where  $T_J$  changed from 25 °C to 125 °C,  $t_1$  increased from 294 ns to 320 ns. The  $T_J$  dependence of  $t_1$  is successfully controlled automatically by the proposed ATC.

Table I shows a comparison table of the closed-loop AGDs. This paper is the first work achieving the fully integrated IC, the real-time control, and the programmable  $I_{\rm G}$  in the closed-loop AGDs.

## **IV.** CONCLUSIONS

The proposed DGD IC with ATC is the first work achieving the fully integrated IC, the real-time control, and the programmable  $I_{\rm G}$  in the closed-loop AGDs. Low  $E_{\rm LOSS}$  and low  $I_{\rm OVERSHOOT}$  can always be achieved at low cost even when the operating conditions, load current ( $I_{\rm L}$ ) and junction temperature ( $T_{\rm J}$ ), change. At  $I_{\rm L}$  = 80 A and  $T_{\rm J}$  = 25 °C,

compared with the conventional SSGD, SGGD with ATC using proposed DGD IC reduces  $E_{\text{LOSS}}$  by 49 % under the  $I_{\text{OVERSHOOT}}$ -aligned condition and reduces  $I_{\text{OVERSHOOT}}$  by 33 % under the  $E_{\text{LOSS}}$ -aligned condition by automatically controlling  $t_1$  and  $t_2$  in real-time.

#### ACKNOWLEDGMENT

This work was partly supported by NEDO (JPNP21009).

#### REFERENCES

- [1] K. Miyazaki, S. Abe, M. Tsukuda, I. Omura, K. Wada, M. Takamiya, and T. Sakurai, "General-purpose clocked gate driver IC with programmable 63-level drivability to optimize overshoot and energy loss in switching by a simulated annealing algorithm," *IEEE Trans. Ind. Appl.*, vol.53, no.3, pp. 2350-2357, May-June 2017.

- [2] W. J. Zhang, J. Yu, Y. Leng, W. T. Cui, G. Q. Deng, and W. T. Ng, "A segmented gate driver for E-mode GaN HEMTs with simple driving strength pattern control," in Proc. IEEE Int. Symp. Power Semicond. Devices ICs, Sep. 2020, pp. 102-105.

- [3] R. Katada, K. Hata, Y. Yamauchi, T. -W. Wang, R. Morikawa, C. -H. Wu, T. Sai, P. -H. Chen, and M. Takamiya, "5 V, 300 MSa/s, 6-bit digital gate driver IC for GaN achieving 69 % reduction of switching loss and 60 % reduction of current overshoot," *in Proc. IEEE Int. Symp. Power Semicond. Devices ICs*, May 2021, pp. 55-58.

- [4] D. Liu, H. C. P. Dymond, S. J. Hollis, J. Wang, N. McNeill, D. Pamunuwa, and B. H. Stark, "Full custom design of an arbitrary waveform gate driver with 10-GHz waypoint rates for GaN FETs," *IEEE Trans. Power Electron.*, vol. 36, no. 7, pp. 8267-8279, July 2021.

- [5] W. J. Zhang, J. Yu, W. T. Cui, Y. Leng, J. Liang, Y.-T. Hsieh, H.-H. Tsai, Y.-Z. Juang, W.-K. Yeh, and W. T. Ng, "A smart gate driver IC for GaN power HEMTs with dynamic ringing suppression," *IEEE Trans. on Power Electronics*, vol. 36, no. 12, pp. 14119-14132, Dec. 2021.

- [6] K. Horii, K. Hata, R. Wang, W. Saito, and M. Takamiya, "Large current output digital gate driver using half-bridge digital-to-analog converter IC and two power MOSFETs," in Proc. IEEE Int. Symp. Power Semicond. Devices ICs, May 2022, pp. 293 – 296.

- [7] V. John, B.-S. Suh, and T. A. Lipo, "High performance active gate drive for high power IGBTs," in Proc. IEEE Industry Applications Conf., Oct. 1998, pp. 1519-1529.

- [8] Y. Sun, L. Sun, A. Esmaeli, and K. Zhao, "A novel three stage drive circuit for IGBT," in Proc. IEEE Conf. on Industrial Electronics and Applications, May 2006, pp. 1-6.

- [9] N. Idir, R. Bausiere, and J. J. Franchaud, "Active gate voltage control of turn-on di/dt and turn-off dv/dt in insulated gate transistors," *IEEE Tran. on Power Electron.*, vol. 21, no. 4, pp. 849-855, July 2006.

- [10] Z. Wang, X. Shi, L. M. Tolbert, F. Wang, and B. J. Blalock, "A di/dt feedback-based active gate driver for smart switching and fast overcurrent protection of IGBT modules," *IEEE Trans. on Power Electron.*, vol. 29, no. 7, pp. 3720-3732, July 2014.

- [11] Y. Lobsiger and J. W. Kolar, "Closed-loop di/dt and dv/dt IGBT gate driver," *IEEE Trans. on Power Electron.*, vol. 30, no. 6, pp. 3402-3417, June 2015.

- [12] F. Zhang, X. Yang, Y. Ren, L. Feng, W. Chen, and Y. Pei, "Advanced active gate drive for switching performance improvement and overvoltage protection of high-power IGBTs," *IEEE Trans. on Power Electron.*, vol. 33, no. 5, pp. 3802-3815, May 2018.

- [13] S. Kawai, T. Ueno, and K. Onizuka, "A 4.5V/ns active slew-ratecontrolling gate driver with robust discrete-time feedback technique for 600V superjunction MOSFETs," *in Proc. IEEE International Solid-State Circuits Conf.*, Feb. 2019, pp. 252-254.

- [14] Y. Wen, Y. Yang, and Y. Gao, "Active gate driver for improving current sharing performance of paralleled high-power SiC MOSFET modules," *IEEE Trans. on Power Electron.*, vol. 36, no. 2, pp. 1491-1505, Feb. 2021.

- [15] Y. Ling, Z. Zhao, and Y. Zhu, "A self-regulating gate driver for highpower IGBTs," *IEEE Trans. on Power Electron.*, vol. 36, no. 3, pp. 3450-3461, March 2021.

- [16] E. Raviola and F. Fiori, "Experimental investigations on the tuning of active gate drivers under load current variations," in Proc. International Conf. on Applied Electronics, Sep. 2021, pp. 1-4.

- [17] M. Sayed, S. Araujo, F. Carraro, and R. Kennel, "Investigation of gate current shaping for SiC-based power modules on electrical drive system power losses," in *Proc. European Conf. on Power Electronics* and *Applications*, Sep. 2021, pp. 1-10.

- [18] J. Zhu, D. Yan, S. Yu, W. Sun, G. Shi, S. Liu, S. Zhang, "A 600V GaN active gate driver with dynamic feedback delay compensation technique achieving 22.5% turn-on energy saving," in Proc. IEEE International Solid-State Circuits Conf., Feb. 2021, pp. 462-464.

- [19] D. Han, S. Kim, X. Dong, H. Li, J. Moon, Y. Li, and F. Peng, "An integrated multi-level active gate driver for SiC power modules," *in Proc. IEEE Transportation Electrification Conf. & Expo.*, June 2022, pp. 727-732.

- [20] T. Sai, K. Miyazaki, H. Obara, T. Mannen, K. Wada, I. Omura, M. Takamiya, and T. Sakurai, "Load current and temperature dependent optimization of active gate driving vectors," in Proc. IEEE Energy Conversion Congress & Exposition, Sep. 2019, pp. 3292-3297.

- [21] T. Sai, K. Miyazaki, H. Obara, T. Mannen, K. Wada, I. Omura, T. Sakurai, and M. Takamiya, "Stop-and-go gate drive minimizing test cost to find optimum gate driving vectors in digital gate drivers," in Proc. IEEE Applied Power Electronics Conf. and Expo., March 2020, pp. 3096-3101

- [22] W. T. Cui, W. J. Zhang, J. Y. Liang, H. Nishio, H. Sumida, H. Nakajima, Y. Hsieh, H. Tsai, Y. Juang, W. Yeh, and W. T. Ng, "A dynamic gate driver IC with automated pattern optimization for SiC power MOSFETs," in Proc. IEEE International Symposium on Power Semiconductor Devices and ICs, May 2022, pp. 33-36.